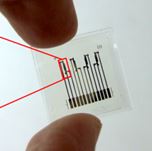

pNeuron

(Printed Electronics for Neuromorphic Computing). In

this project, funded by the EPSRC Centre for

Inoovative Manufacturing in Large-Area Electronics, under the

Pathfinder scheme,

we investigated the implementation of spiking neuron circuits,

mimicking biological behaviour, using printed electronics technology.

Furter details about the project can be found here.

pNeuron

(Printed Electronics for Neuromorphic Computing). In

this project, funded by the EPSRC Centre for

Inoovative Manufacturing in Large-Area Electronics, under the

Pathfinder scheme,

we investigated the implementation of spiking neuron circuits,

mimicking biological behaviour, using printed electronics technology.

Furter details about the project can be found here.

|

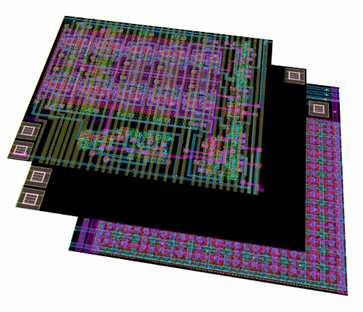

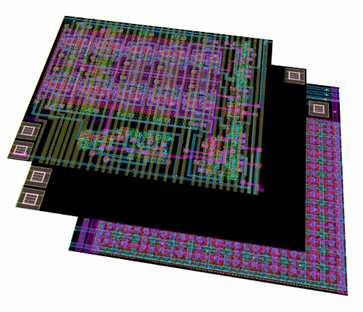

FINE3D

(Fine-Grain Processor Arrays in 3D Silicon Technologies). In this

project, funded by the EPSRC, we investigated the design of

cellular processor arrays for next-generation silicon technologies,

where many device layers can be integrated in a single device. Wafer

stacking and massive interconnect achieved using through-silicon-vias

provides both opportunities and design challenges. We researched

processor architectures that make best use of the available intra-layer

bandwidth, investigated partitioning of the processing circuitry

amongst silicon layers, and looked into heterogenous architectures

where different layers are fabricated using different technologies,

most suitable for individual system components. In particular, we are

interested in fine-grain processor arrays, which we believe provide

architectural solution that can fully exploit the benefits offered by

the 3D integration.

FINE3D

(Fine-Grain Processor Arrays in 3D Silicon Technologies). In this

project, funded by the EPSRC, we investigated the design of

cellular processor arrays for next-generation silicon technologies,

where many device layers can be integrated in a single device. Wafer

stacking and massive interconnect achieved using through-silicon-vias

provides both opportunities and design challenges. We researched

processor architectures that make best use of the available intra-layer

bandwidth, investigated partitioning of the processing circuitry

amongst silicon layers, and looked into heterogenous architectures

where different layers are fabricated using different technologies,

most suitable for individual system components. In particular, we are

interested in fine-grain processor arrays, which we believe provide

architectural solution that can fully exploit the benefits offered by

the 3D integration.

|

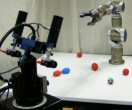

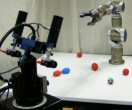

REVERB

(Reverse Engineering

the Vertebrate Brain). This

project was a multidisciplinary collaboration between a number of

universities (Manchester, Sheffield, Aberystwyth, Bristol, Dundee)

investigating integrative computation for autonomous agents, based on

action-selection architecture of the basal ganglia. We were

implementing low-level image processing required for this project, as

well as some neural models, using SCAMP-3 and SCAMP-4 chips. We were

also working towards an FPGA-based accelerator for neural computation,

to tackle the real-time embedded implementation on an autonomous robot.

We developed the APRON

(Array Programming Environment) software, as a front-end to

the accelerator. The software is also an efficient simulation tool on

its own, furthermore it provides a basis for platform-independent array

processor interface, programming language, and code compiler, and has

been adopted to work with SCAMP and ASPA chips. See REVERB project webpage

for details.

REVERB

(Reverse Engineering

the Vertebrate Brain). This

project was a multidisciplinary collaboration between a number of

universities (Manchester, Sheffield, Aberystwyth, Bristol, Dundee)

investigating integrative computation for autonomous agents, based on

action-selection architecture of the basal ganglia. We were

implementing low-level image processing required for this project, as

well as some neural models, using SCAMP-3 and SCAMP-4 chips. We were

also working towards an FPGA-based accelerator for neural computation,

to tackle the real-time embedded implementation on an autonomous robot.

We developed the APRON

(Array Programming Environment) software, as a front-end to

the accelerator. The software is also an efficient simulation tool on

its own, furthermore it provides a basis for platform-independent array

processor interface, programming language, and code compiler, and has

been adopted to work with SCAMP and ASPA chips. See REVERB project webpage

for details.

|

COLAMN

(Computing Architecture Based on Laminar Microcircuitry of the

Neocortex).

This project was a collaboration between neurobiologists, computational

neuroscientists and VLSI engineers (Manchester, Plymouth, Cambridge,

Oxford) aiming at understanding the way cortical circuits process

information, and ultimately providing ideas for building brain-inspired

microelectronic circuits. We have developed an analogue silicon neuron,

which efficiently implements biologically plausible spiking behaviour

of cortical neurons. Currently we are investigating higher-level

cognitive models of the cortex, and their VLSI implementation. more...

COLAMN

(Computing Architecture Based on Laminar Microcircuitry of the

Neocortex).

This project was a collaboration between neurobiologists, computational

neuroscientists and VLSI engineers (Manchester, Plymouth, Cambridge,

Oxford) aiming at understanding the way cortical circuits process

information, and ultimately providing ideas for building brain-inspired

microelectronic circuits. We have developed an analogue silicon neuron,

which efficiently implements biologically plausible spiking behaviour

of cortical neurons. Currently we are investigating higher-level

cognitive models of the cortex, and their VLSI implementation. more...

|

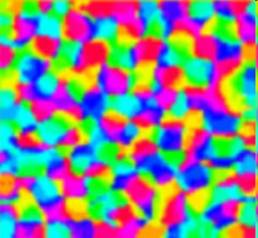

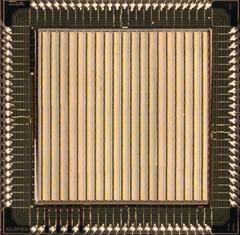

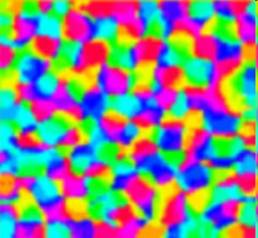

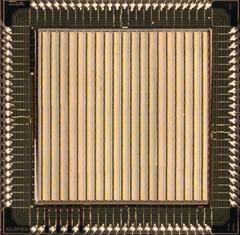

Cellular Asynchronous Arrays.

This project investigates design of vision chips and

fine-grain

processor arrays based on novel control schemes, where individual

processors are triggered as data is available at their neighbours,

optimising speed and power consumption of the devices. The aim is to

provide image processing engines suitable for both low-level,

pixel-based operations (filtering, feature detection etc.) as well as

more global, object-based algorithms, such as object reconstruction,

skeletonisation, watarshed transform, distance transform etc. The ASPA

chip contains a SIMD processor array, operating in mixed

bit-serial/bit-parallel mode, as well as a wave-propagating network.

The work continues on next generation of the ASPA processor in the

Fine-Grain 3D project. more...

Cellular Asynchronous Arrays.

This project investigates design of vision chips and

fine-grain

processor arrays based on novel control schemes, where individual

processors are triggered as data is available at their neighbours,

optimising speed and power consumption of the devices. The aim is to

provide image processing engines suitable for both low-level,

pixel-based operations (filtering, feature detection etc.) as well as

more global, object-based algorithms, such as object reconstruction,

skeletonisation, watarshed transform, distance transform etc. The ASPA

chip contains a SIMD processor array, operating in mixed

bit-serial/bit-parallel mode, as well as a wave-propagating network.

The work continues on next generation of the ASPA processor in the

Fine-Grain 3D project. more...

|

FINE3D

(Fine-Grain Processor Arrays in 3D Silicon Technologies). In this

project, funded by the EPSRC, we investigated the design of

cellular processor arrays for next-generation silicon technologies,

where many device layers can be integrated in a single device. Wafer

stacking and massive interconnect achieved using through-silicon-vias

provides both opportunities and design challenges. We researched

processor architectures that make best use of the available intra-layer

bandwidth, investigated partitioning of the processing circuitry

amongst silicon layers, and looked into heterogenous architectures

where different layers are fabricated using different technologies,

most suitable for individual system components. In particular, we are

interested in fine-grain processor arrays, which we believe provide

architectural solution that can fully exploit the benefits offered by

the 3D integration.

FINE3D

(Fine-Grain Processor Arrays in 3D Silicon Technologies). In this

project, funded by the EPSRC, we investigated the design of

cellular processor arrays for next-generation silicon technologies,

where many device layers can be integrated in a single device. Wafer

stacking and massive interconnect achieved using through-silicon-vias

provides both opportunities and design challenges. We researched

processor architectures that make best use of the available intra-layer

bandwidth, investigated partitioning of the processing circuitry

amongst silicon layers, and looked into heterogenous architectures

where different layers are fabricated using different technologies,

most suitable for individual system components. In particular, we are

interested in fine-grain processor arrays, which we believe provide

architectural solution that can fully exploit the benefits offered by

the 3D integration.

REVERB

(Reverse Engineering

the Vertebrate Brain). This

project was a multidisciplinary collaboration between a number of

universities (Manchester, Sheffield, Aberystwyth, Bristol, Dundee)

investigating integrative computation for autonomous agents, based on

action-selection architecture of the basal ganglia. We were

implementing low-level image processing required for this project, as

well as some neural models, using SCAMP-3 and SCAMP-4 chips. We were

also working towards an FPGA-based accelerator for neural computation,

to tackle the real-time embedded implementation on an autonomous robot.

We developed the

REVERB

(Reverse Engineering

the Vertebrate Brain). This

project was a multidisciplinary collaboration between a number of

universities (Manchester, Sheffield, Aberystwyth, Bristol, Dundee)

investigating integrative computation for autonomous agents, based on

action-selection architecture of the basal ganglia. We were

implementing low-level image processing required for this project, as

well as some neural models, using SCAMP-3 and SCAMP-4 chips. We were

also working towards an FPGA-based accelerator for neural computation,

to tackle the real-time embedded implementation on an autonomous robot.

We developed the  COLAMN

(Computing Architecture Based on Laminar Microcircuitry of the

Neocortex).

This project was a collaboration between neurobiologists, computational

neuroscientists and VLSI engineers (Manchester, Plymouth, Cambridge,

Oxford) aiming at understanding the way cortical circuits process

information, and ultimately providing ideas for building brain-inspired

microelectronic circuits. We have developed an analogue silicon neuron,

which efficiently implements biologically plausible spiking behaviour

of cortical neurons. Currently we are investigating higher-level

cognitive models of the cortex, and their VLSI implementation.

COLAMN

(Computing Architecture Based on Laminar Microcircuitry of the

Neocortex).

This project was a collaboration between neurobiologists, computational

neuroscientists and VLSI engineers (Manchester, Plymouth, Cambridge,

Oxford) aiming at understanding the way cortical circuits process

information, and ultimately providing ideas for building brain-inspired

microelectronic circuits. We have developed an analogue silicon neuron,

which efficiently implements biologically plausible spiking behaviour

of cortical neurons. Currently we are investigating higher-level

cognitive models of the cortex, and their VLSI implementation.  Cellular Asynchronous Arrays.

This project investigates design of vision chips and

fine-grain

processor arrays based on novel control schemes, where individual

processors are triggered as data is available at their neighbours,

optimising speed and power consumption of the devices. The aim is to

provide image processing engines suitable for both low-level,

pixel-based operations (filtering, feature detection etc.) as well as

more global, object-based algorithms, such as object reconstruction,

skeletonisation, watarshed transform, distance transform etc. The ASPA

chip contains a SIMD processor array, operating in mixed

bit-serial/bit-parallel mode, as well as a wave-propagating network.

The work continues on next generation of the ASPA processor in the

Fine-Grain 3D project.

Cellular Asynchronous Arrays.

This project investigates design of vision chips and

fine-grain

processor arrays based on novel control schemes, where individual

processors are triggered as data is available at their neighbours,

optimising speed and power consumption of the devices. The aim is to

provide image processing engines suitable for both low-level,

pixel-based operations (filtering, feature detection etc.) as well as

more global, object-based algorithms, such as object reconstruction,

skeletonisation, watarshed transform, distance transform etc. The ASPA

chip contains a SIMD processor array, operating in mixed

bit-serial/bit-parallel mode, as well as a wave-propagating network.

The work continues on next generation of the ASPA processor in the

Fine-Grain 3D project.