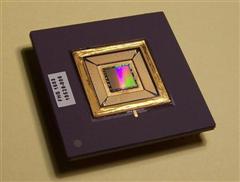

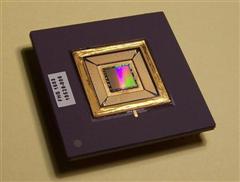

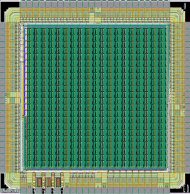

Vision

chips are microelectronic devices, which combine image sensing and

processing on a single silicon die. In a way somewhat resembling the

vertebrate retina, these semiconductor chips perform preliminary image

processing directly on the sensory plane. They can be used for computer vision

applications in areas such as autonomous vehicle guidance, robotics,

industrial inspection or surveillance. We investigate the

design of vision chips, using CMOS technologies. Integrating a

processing element (PE) within each pixel of the image sensor array results in

thousands of processors working concurrently, which enables the processing

speeds of billions of operations per second to be easily achieved,

at very low power consumption. Vision

chips are microelectronic devices, which combine image sensing and

processing on a single silicon die. In a way somewhat resembling the

vertebrate retina, these semiconductor chips perform preliminary image

processing directly on the sensory plane. They can be used for computer vision

applications in areas such as autonomous vehicle guidance, robotics,

industrial inspection or surveillance. We investigate the

design of vision chips, using CMOS technologies. Integrating a

processing element (PE) within each pixel of the image sensor array results in

thousands of processors working concurrently, which enables the processing

speeds of billions of operations per second to be easily achieved,

at very low power consumption.

|

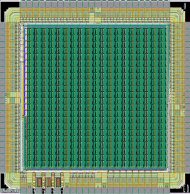

Cellular processors arrays offer high computing performance and are ideally

suited to perform pixel-parallel image processing tasks. Our research focuses

on computer architectures based on fine-grain SIMD processor arrays and asynchronous

cellular automata. We have developed several approaches, e.g. SCAMP is family

of mixed-mode pixel-per-processor SIMD array devices while ASPA devices are

massively parallel processor

arrays which work in asynchronous/synchronous mode running wave-propagating

algorithms. We implement integrated circuits in state-of the-art and emerging

silicon technologies, such as sub-100nm CMOS and stacked 3D wafers. Cellular processors arrays offer high computing performance and are ideally

suited to perform pixel-parallel image processing tasks. Our research focuses

on computer architectures based on fine-grain SIMD processor arrays and asynchronous

cellular automata. We have developed several approaches, e.g. SCAMP is family

of mixed-mode pixel-per-processor SIMD array devices while ASPA devices are

massively parallel processor

arrays which work in asynchronous/synchronous mode running wave-propagating

algorithms. We implement integrated circuits in state-of the-art and emerging

silicon technologies, such as sub-100nm CMOS and stacked 3D wafers.

|

Brain-inspired

VLSI circuits may one day replace conventional microprocessors as more

robust and intelligent systems. They will be also used as controllers for

autonomous robots, and in prosthetic devices. We research digital FPGA based,

and analogue full-custom VLSI based acceleration engines for neural

computation. Currently we participate in two

collaborative projects, REVERB and COLAMN, supported under the EPSRC Novel

Computation Initiative, where we work with neuroscientists,

psychologists and computer scientists, investigating computation in biological

neural networks and designing neuromorphic chips and systems implementing

natural computation in hardware. Brain-inspired

VLSI circuits may one day replace conventional microprocessors as more

robust and intelligent systems. They will be also used as controllers for

autonomous robots, and in prosthetic devices. We research digital FPGA based,

and analogue full-custom VLSI based acceleration engines for neural

computation. Currently we participate in two

collaborative projects, REVERB and COLAMN, supported under the EPSRC Novel

Computation Initiative, where we work with neuroscientists,

psychologists and computer scientists, investigating computation in biological

neural networks and designing neuromorphic chips and systems implementing

natural computation in hardware.

|

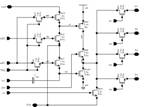

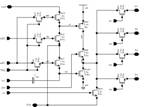

Analogue

signal processing circuits can offer higher efficiency (in terms of

performance, silicon area and power dissipation) than their digital

counterparts. We investigate algorithmically programmable general-purpose

analogue microprocessors build using switched-current circuit techniques

and analogue implementations of spiking neural networks. We are interested in

ultra-low power computing hardware. We are also developing sensors, sensor

interface circuits and signal processing circuits

for biomedical applications, such as high-frequency medical ultrasound

systems. Analogue

signal processing circuits can offer higher efficiency (in terms of

performance, silicon area and power dissipation) than their digital

counterparts. We investigate algorithmically programmable general-purpose

analogue microprocessors build using switched-current circuit techniques

and analogue implementations of spiking neural networks. We are interested in

ultra-low power computing hardware. We are also developing sensors, sensor

interface circuits and signal processing circuits

for biomedical applications, such as high-frequency medical ultrasound

systems.

|

Novel

algorithms need to be developed to take full advantage of the massively

parallel hardware. We investigate ways of efficiently mapping low- and

mid-level image processing algorithms onto processor arrays. We are interested

in computer vision and machine intelligence, especially in the context of

autonomous robots. We work on brain-inspired algorithms for object recognition

and efficient simulation of large biologically plausible neural network models

using a range of techniques including processing using GPUs and other parallel

hardware as well as custom processors. We are also

developing systems and software tools for controlling and programming

fine-grain processor arrays and vision chips Novel

algorithms need to be developed to take full advantage of the massively

parallel hardware. We investigate ways of efficiently mapping low- and

mid-level image processing algorithms onto processor arrays. We are interested

in computer vision and machine intelligence, especially in the context of

autonomous robots. We work on brain-inspired algorithms for object recognition

and efficient simulation of large biologically plausible neural network models

using a range of techniques including processing using GPUs and other parallel

hardware as well as custom processors. We are also

developing systems and software tools for controlling and programming

fine-grain processor arrays and vision chips

|

Vision

chips are microelectronic devices, which combine image sensing and

processing on a single silicon die. In a way somewhat resembling the

vertebrate retina, these semiconductor chips perform preliminary image

processing directly on the sensory plane. They can be used for computer vision

applications in areas such as autonomous vehicle guidance, robotics,

industrial inspection or surveillance.

Vision

chips are microelectronic devices, which combine image sensing and

processing on a single silicon die. In a way somewhat resembling the

vertebrate retina, these semiconductor chips perform preliminary image

processing directly on the sensory plane. They can be used for computer vision

applications in areas such as autonomous vehicle guidance, robotics,

industrial inspection or surveillance.  Cellular processors arrays offer high computing performance and are ideally

suited to perform pixel-parallel image processing tasks. Our research focuses

on computer architectures based on fine-grain SIMD processor arrays and asynchronous

cellular automata. We have developed several approaches, e.g. SCAMP is family

of mixed-mode pixel-per-processor SIMD array devices while ASPA devices are

massively parallel processor

arrays which work in asynchronous/synchronous mode running wave-propagating

algorithms. We implement integrated circuits in state-of the-art and emerging

silicon technologies, such as sub-100nm CMOS and stacked 3D wafers

Cellular processors arrays offer high computing performance and are ideally

suited to perform pixel-parallel image processing tasks. Our research focuses

on computer architectures based on fine-grain SIMD processor arrays and asynchronous

cellular automata. We have developed several approaches, e.g. SCAMP is family

of mixed-mode pixel-per-processor SIMD array devices while ASPA devices are

massively parallel processor

arrays which work in asynchronous/synchronous mode running wave-propagating

algorithms. We implement integrated circuits in state-of the-art and emerging

silicon technologies, such as sub-100nm CMOS and stacked 3D wafers Brain-inspired

VLSI circuits may one day replace conventional microprocessors as more

robust and intelligent systems. They will be also used as controllers for

autonomous robots, and in prosthetic devices. We research digital FPGA based,

and analogue full-custom VLSI based acceleration engines for neural

computation.

Brain-inspired

VLSI circuits may one day replace conventional microprocessors as more

robust and intelligent systems. They will be also used as controllers for

autonomous robots, and in prosthetic devices. We research digital FPGA based,

and analogue full-custom VLSI based acceleration engines for neural

computation.  Analogue

signal processing circuits can offer higher efficiency (in terms of

performance, silicon area and power dissipation) than their digital

counterparts. We investigate algorithmically programmable general-purpose

analogue microprocessors build using switched-current circuit techniques

Analogue

signal processing circuits can offer higher efficiency (in terms of

performance, silicon area and power dissipation) than their digital

counterparts. We investigate algorithmically programmable general-purpose

analogue microprocessors build using switched-current circuit techniques Novel

algorithms need to be developed to take full advantage of the massively

parallel hardware. We investigate ways of efficiently mapping low- and

mid-level image processing algorithms onto processor arrays. We are interested

in computer vision and machine intelligence, especially in the context of

autonomous robots. We work on brain-inspired algorithms for object recognition

and efficient simulation of large biologically plausible neural network models

using a range of techniques including processing using GPUs and other parallel

hardware as well as custom processors.

Novel

algorithms need to be developed to take full advantage of the massively

parallel hardware. We investigate ways of efficiently mapping low- and

mid-level image processing algorithms onto processor arrays. We are interested

in computer vision and machine intelligence, especially in the context of

autonomous robots. We work on brain-inspired algorithms for object recognition

and efficient simulation of large biologically plausible neural network models

using a range of techniques including processing using GPUs and other parallel

hardware as well as custom processors.