## Demonstration of real-time image processing on the SCAMP-3 vision system

Piotr Dudek, David R.W. Barr, Alexey Lopich and Stephen J. Carey

School of Electrical and Electronic Engineering, University of Manchester, e-mail: p.dudek@ manchester.ac.uk

Abstract - Vision system based on a cellular processor array integrated circuit is presented. The system includes the SCAMP-3 vision chip, control and interface circuits, and software development environment enabling code simulation, compilation and debugging. Execution of a number of low-level image processing algorithms in real-time is demonstrated.

## INTRODUCTION

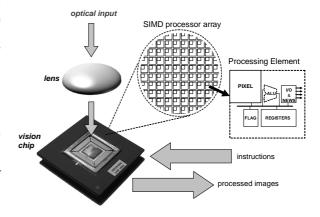

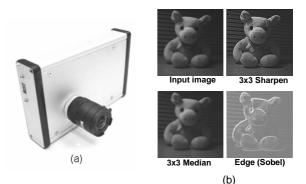

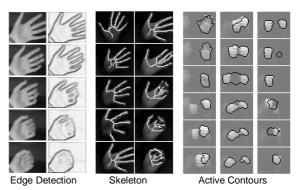

The Cellular Neural Network (CNN) model is believed to provide a useful paradigm for designing VLSI image processing systems, specifically pixel-parallel vision processors. Our work demonstrates that a device based on a different concept, that of a massively parallel array of simple sequential analogue processors, operating in a Single Instruction Multiple Data (SIMD) mode, can achieve superior performance as compared with CNN-UM chips when applied to common image processing problems [1,2]. We have recently developed the SCAMP-3 vision chip (Fig.1), which implements a 128x128 cellular processor array [3]. We have also developed a system, based on the vision chip (Fig.2a), which includes controller and interface electronics [4]. The software controlling the vision system supports algorithm development, simulation, compilation and host communication. The general-purpose nature of the system allows the implementation of many low-level image processing algorithm, examples of which are shown in Fig.2b. Filtering and feature detectors based on 3x3 convolution kernels are easily implemented. Other popular CNN-type operators, based on propagating templates (such as hole-filling), are implemented iteratively. Non-linear filtering (e.g. true median filter) as well as more complex algorithms (e.g. skeletonization and active contours, shown in Fig.3) can be implemented and executed at high frame rates and with low power consumption. These features will be demonstrated during the live session.

## REFERENCES

- [1] P.Dudek and P.J.Hicks, "A General-Purpose Processor-per-Pixel Analog SIMD Vision Chip", IEEE Transactions on Circuits and Systems - I, vol. 52, no. 1, pp. 13-20, January 2005

- [2] P.Dudek, "Accuracy and Efficiency of Grey-level Image Filtering on VLSI Cellular Processor Arrays", IEEE Workshop on Cellular Neural Networks and their Applications, CNNA 2004, Budapest, pp.123-128, Budapest, July 2004

- [3] P.Dudek, "Implementation of SIMD Vision Chip with 128x128 Array of Analogue Processing Elements", IEEE International Symposium on Circuits and Systems, ISCAS 2005, Kobe, pp.5806-5809, May 2005

- [4] D.R.W.Barr, S.J.Carey, A.Lopich and P. Dudek, "A Control System for a Cellular Processing Array Vision Chip", IEEE Workshop on Cellular Neural Networks and their Applications, CNNA 2006.

Fig.1. Overview of the SIMD pixel-parallel cellular vision chip

Fig.2. (a) SCAMP vision system (b) Processing results

Fig.3. Processing of real-time image sequences (experimental results from 39x48 array chip are shown)