ARCHIVE This in an archive page, describing the SCAMP chips developed at UMIST (now The University of Manchester) between 2001-2005. For more recent developments of this technology, please see SCAMP-5 vision chip website here

Vision chips integrate image sensing and processing on a single silicon die. In a way somewhat resembling the vertebrate retina, these semiconductor chips perform preliminary image processing directly on the focal plane, integrating a processing element within each pixel of the image sensor array. The array operates in SIMD (Single Instruction Multiple Data) mode. Processing elements simultaneously execute identical instructions on their local data. The processors can also exchange information with their nearest neighbours. Each processing element, is a simple, but complete processor, comprising Arithmetic Logic Unit, Memory, Local Control and I/O ports and also include a photodetector.

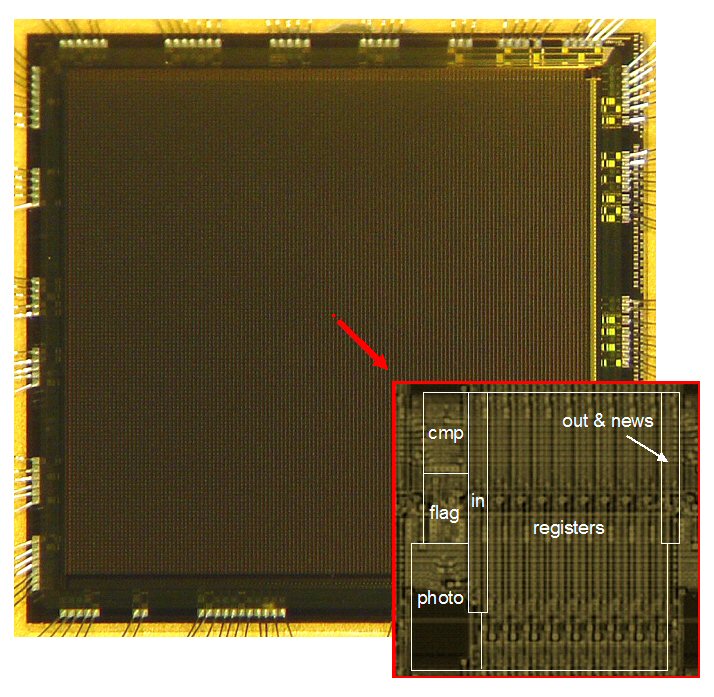

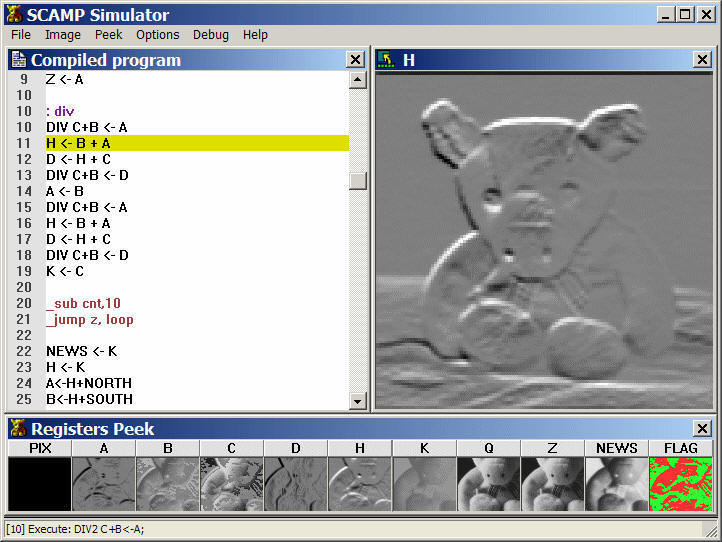

In a high-resolution pixel-parallel SIMD vision chip the silicon area available for each processing element is very limited. Our key idea is the introduction of an analogue processing element (APE). The APE executes software instructions in a manner akin to a digital processor, but it operates on analogue samples of data. Compact registers are build using switched-current storage cells, arithmetic operations are performed without any extra hardware: adder circuit is replaced by current summation on the bus wire (Kirchhoff’s law). This combination of analogue circuitry and digital architecture results in unprecedented efficiency in terms of performance, cost and power dissipation. The SCAMP-3 chip, fabricated in a 0.35 um CMOS technology contained a 128x128 processor array (a single cell measures under 50um x 50um). operating with a 1.25 MHz clock and maximum power consumption of 12 uW/cell.

Image Processing Examples:

Edge detection (Sobel): processing time 30us, power consumption 73nW/pixel @ 25 fps Movie (3 MB))

Motion Detection: Movie (3 MB)

Active Contours - Pixel Level Snakes (up to 30 evolutions per frame at 30 frames per second!: Movie1 (20 MB), Movie2 (.avi, 8 MB)

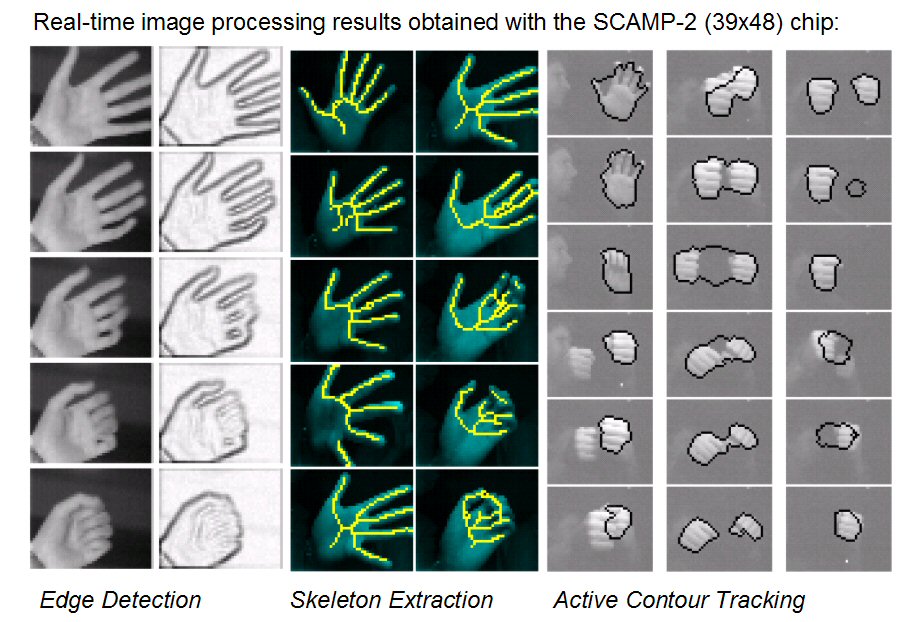

SCAMP-3 system ("Silver Box") provided all control and interface circuits for the vision chip, with a USB 2.0 based interface for development and parallel interface for custom hardware. The software included Simulator/Development Environment, Graphical User Interface and Windows and Linix versions of Software Framework for custom applications.

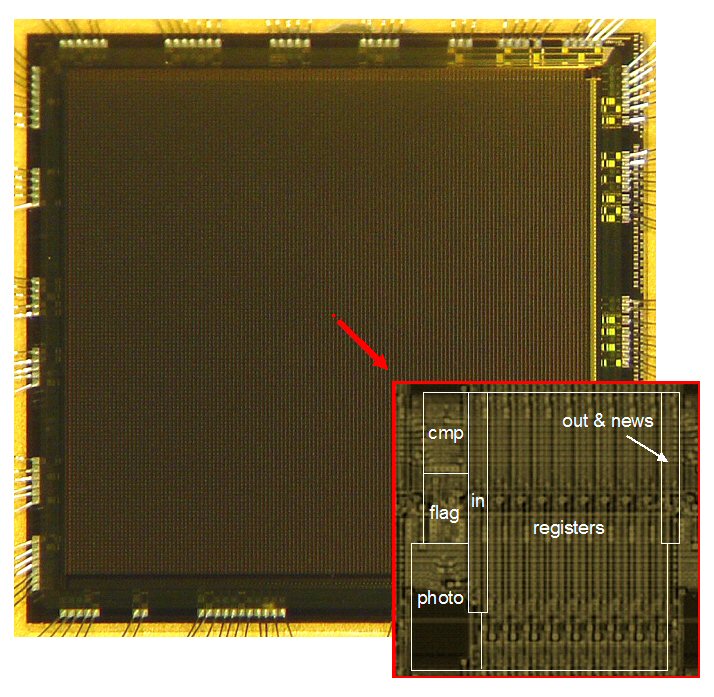

SCAMP-2 was a general-purpose programmable vision chip with a 39x48 SIMD processor-per-pixel array fabricated in a 0.35um CMOS technology. Some of the experimental results obtained from the chip are presented below:

Edge detection algorithm: processing time 30us, power consumption 73nW/pixel @ 25 fps

Median filtering algorithm: processing time 157us, power consumption 380nW/pixel @ 25 fps

Cellular Automata - Game of Life

Greenberg-Hastings Model of Excitable Medium

Movie (.avi, compressed, 0.3 MB)

Movie (.avi, compressed, 0.3 MB)

Active Contours - Pixel Level Snakes

Skeletons

Dr Piotr Dudek, School of Electrical and Electronic Engineering, The University of Manchester, PO Box 88, Manchester M60 1QD, UK, Email: p.dudek@manchester.ac.uk