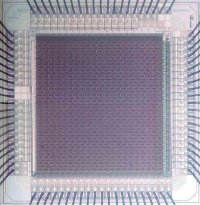

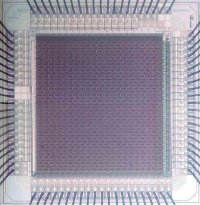

chip photo (417kB)

chip photo (417kB) chip photo (417kB)

chip photo (417kB)

SCAMP is a software-programmable massively parallel processor operating in the SIMD (Single Instruction Multiple Data) mode. It contains a 21x21 mesh-connected array of processing elements, which execute instructions issued by a single digital controller. A wide class of low-level image processing algorithms can be implemented efficiently, exploiting inherent fine-grain parallelism of these tasks. When executing image processing algorithms, a single processing element is associated with a single pixel in the image.

Fig.1. The 2-D mesh-connected array (fragment)

Each processing element of the SCAMP chip integrates a photodetector, so that the images are input to the processor array optically. This integration removes the I/O bottleneck between the sensor and the processor, reduces size, cost and power dissipation of the system. The images are processed directly on the focal-plane. The chip is therefore a 'smart sensor' or a 'focal-plane processor'.

Fig.2. Programmable focal-plane processor principle

To implement a fine-grain software-programmable processor array a compact yet versatile processing element is needed. In the SCAMP chip, the processing nodes utilise the analogue microprocessor concept, which enables the achievement of excellent performance/power and performance/area ratios. The processing element size is below 100umX100um, nevertheless it is a fully software-programmable entity. Instruction set includes load/store, addition, subtraction, multiplication, neighbour communication, conditional disable, parallel input and random-addressable output. Processing is performed on sampled-data analogue signals using switched-current circuit techniques (analogue computations are characterised by limited accuracy, however in many cases early vision algorithms do not require great precision).

Fig.3. The architecture of the processing element

SCAMP chip is currently

programmed at the machine-level. The programming environment includes:

- program editor (with syntax checking),

- software simulator (which includes debugging facilities and analogue error

modeling),

- code generator (which generates binary code from the symbolic machine-level

language).

When running programs on the SCAMP chip a laboratory data generator is currently used as an external controller. The processed images are read-out from the SCAMP chip using a PC with a parallel interface.

Several low-level image processing algorithms have been implemented to demonstrate the performance of the chip. Some examples of the processing results are presented below:

Correlated double sampling is implemented in software, to reduce fixed pattern noise.

|

|

|

|

(See machine-level source code)

|

Input image |

Edge detection result |

|

Result for a stationary image |

Result for a moving cross object |

|

Input image |

Processing result |

|

Image corrupted by noise |

Processing result |

For comparison: result of median filter computed on a digital processor |

Massively parallel processing results in high computational power. All above algorithms and many more, e.g. smoothing, segmentation, adaptive thresholding, histogram modifications, optical flow (block matching), etc. are easily performed in real-time. For example, Sobel edge detection is performed in 12us, median filter is performed in 62us. Power dissipation, at 30 frames/sec, is below 0.125uW per pixel.

SCAMP chip is a research vehicle, and serves as the demonstration of the capabilities of the technique. However, the architecture is scalable, and it is feasible to fit even quite large arrays (e.g. 256x256 pixels) onto a single die in present-day CMOS technologies. The SCAMP approach can be used to implement front-end for a low-cost, low-power, high performance, versatile vision systems.

Further developments: SCAMP-2 and SCAMP-3