ASPA - Asynchronous/Synchronous Cellular Processor

Array

This project investigates design of vision

chips and fine-grain processor arrays based on novel control schemes,

where individual processors are triggered as data is available at their

neighbours, optimising speed and power consumption of the devices. The

aim is to provide image processing engines suitable for both low-level,

pixel-based operations (filtering, feature detection etc.) as well as

more global, object-based algorithms, such as object reconstruction,

skeletonisation, watarshed transform, distance transform etc. The ASPA

chip contains a SIMD processor array, operating in mixed

bit-serial/bit-parallel mode, as well as a wave-propagating

network.

This project investigates design of vision

chips and fine-grain processor arrays based on novel control schemes,

where individual processors are triggered as data is available at their

neighbours, optimising speed and power consumption of the devices. The

aim is to provide image processing engines suitable for both low-level,

pixel-based operations (filtering, feature detection etc.) as well as

more global, object-based algorithms, such as object reconstruction,

skeletonisation, watarshed transform, distance transform etc. The ASPA

chip contains a SIMD processor array, operating in mixed

bit-serial/bit-parallel mode, as well as a wave-propagating

network.

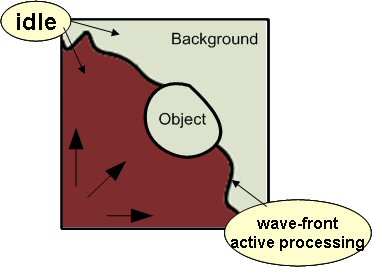

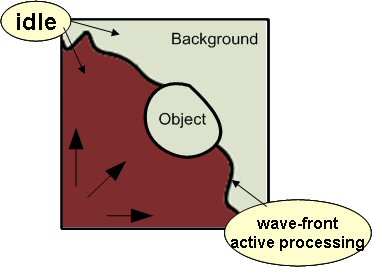

Wave

Propagation Computing

In a wave-propagating array, individual processors are

activated by data-flow, as neighbours complete their computations. This results in high efficiency

as compared with SIMD processor array for

algorithms such as trigger-waves,

distance transforms, skeletons, etc.

Integrate

Circuit Prototypes

The first

proof-of-concept ASPA

chip has been fabricated in 0.35um CMOS technology. The

performance of a single PE is 10 MOPS (gray-scale additions) 83 MOPS

(binary operations) and 2.9 GOPS (binary propagations, as compared with

SIMD array). The chip efficiently executes wave-propagation based

algorithms - in addition to functioning as a general purpose fine-grain

processor array, suitable for real-time image processing and other

array based computations. It also integrates image sensors in a

pixel-per-processor architecture.

The first

proof-of-concept ASPA

chip has been fabricated in 0.35um CMOS technology. The

performance of a single PE is 10 MOPS (gray-scale additions) 83 MOPS

(binary operations) and 2.9 GOPS (binary propagations, as compared with

SIMD array). The chip efficiently executes wave-propagation based

algorithms - in addition to functioning as a general purpose fine-grain

processor array, suitable for real-time image processing and other

array based computations. It also integrates image sensors in a

pixel-per-processor architecture.

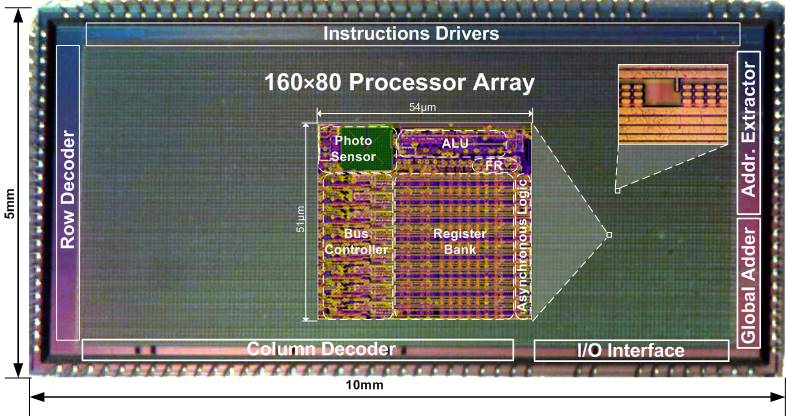

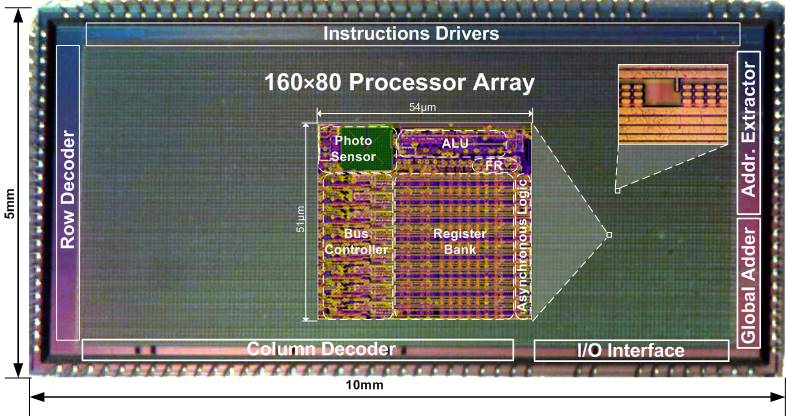

The

second generation ASPA-2 chip

has been

designed

in a 180nm CMOS technology. It contains 80x80 processor array, with

synchronous SIMD and asynchronous wave-propagating mode. Peripherial

circuits perform coordinate address extraction for efficient object

localisation and tracking

The

latest chip in this family,

ASPA-3, has a 160x80 processor array.

The

chip is fabricated in a 180nm CMOS technology. It is a vision chip,

including a pixel-parallel SIMD cellular processor array operating in a

synchronous mode, as well as asynchronous propagation circuits.

Future

Work

We

are continuing our work on pixel-parallel cellular processor array in

the recently-funded EPSRC project on

"Fine-Grain Processor Arrays in 3D Silicon Technologies (FINE3D)"

Publications:

A.Lopich and P.Dudek, "A SIMD Cellular Processor Array Vision Chip With Asynchronous Processing Capabilities", IEEE Transactions on Circuits and Systems - I, vol 58, issue 10, pp. 2420-2431, October 2011

A.Lopich and P.Dudek, "Asynchronous Cellular Logic Network as a Co-Processor for a General-Purpose Massively Parallel Array",International Journal of Circuit Theory and Applications, Volume 39, Issue 9, pages 963–972, September 2011

A.Lopich and

P.Dudek, Hardware

Implementation of Skeletonization Algorithm for Parallel Asynchronous

Image Processing, Journal of Signal

Processing Systems, Springer, Volume 56, Number 1,

pp. 91-103, July 2009

A.Lopich

and P.Dudek, "ASPA:

Focal Plane Digital Processor Array with Asynchronous Processing

Capabilities", IEEE International Symposium on Circuits and

Systems, ISCAS 2008, pp 1592-1596, May 2008

A.Lopich and P.Dudek, "Implementation

of an Asynchronous Cellular Logic Network as a Co-Processor for a

General-Purpose Massively Parallel Array", European

Conference on Circuit Theory and Design, ECCTD 2007, pp.84-87, Seville,

Spain, August 2007

A.Lopich

and P.Dudek, “Global

operations on SIMD cellular processor arrays: towards functional

asynchronism”, International Workshop on Computer

Architectures for Machine Perception and Sensing, CAMPS 2006, pp.18-23,

September 2006

P.Dudek,

"An

Asynchronous Cellular Logic Network for Trigger-Wave Image Processing

on Fine-Grain Massively Parallel Arrays", IEEE

Transactions on Circuits and Systems - II, vol. 53, no.5, pp.

354-358, May 2006

Dr Piotr Dudek, School of

Electrical and Electronic Engineering, The University of Manchester, PO

Box 88, Manchester M60 1QD, UK, Email: p.dudek@manchester.ac.uk

This project investigates design of vision

chips and fine-grain processor arrays based on novel control schemes,

where individual processors are triggered as data is available at their

neighbours, optimising speed and power consumption of the devices. The

aim is to provide image processing engines suitable for both low-level,

pixel-based operations (filtering, feature detection etc.) as well as

more global, object-based algorithms, such as object reconstruction,

skeletonisation, watarshed transform, distance transform etc. The ASPA

chip contains a SIMD processor array, operating in mixed

bit-serial/bit-parallel mode, as well as a wave-propagating

network.

This project investigates design of vision

chips and fine-grain processor arrays based on novel control schemes,

where individual processors are triggered as data is available at their

neighbours, optimising speed and power consumption of the devices. The

aim is to provide image processing engines suitable for both low-level,

pixel-based operations (filtering, feature detection etc.) as well as

more global, object-based algorithms, such as object reconstruction,

skeletonisation, watarshed transform, distance transform etc. The ASPA

chip contains a SIMD processor array, operating in mixed

bit-serial/bit-parallel mode, as well as a wave-propagating

network.  The first

proof-of-concept

The first

proof-of-concept